今日,从国家知识产权局官网获悉,华为公开了一种芯片堆叠封装及终端设备专利,申请公布号为,可解决因采用硅通孔技术而导致的成本高的问题。

专利摘要显示封装,该专利涉及半导体技术领域,其能够在保证供电需求的同时,解决因采用硅通孔技术而导致的成本高的问题。

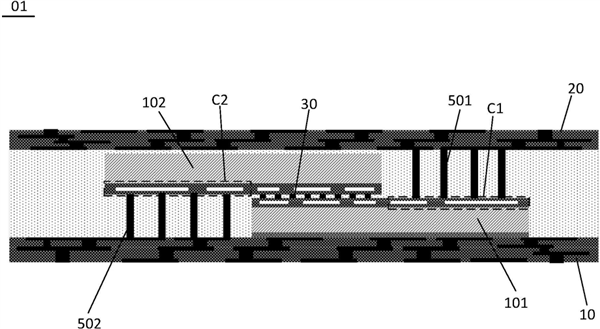

具体来看封装,该芯片堆叠封装(01)包括:

设置于第一走线结构(10)和第二走线结构(20)之间的第一芯片(101)和第二芯片(102);

所述第一芯片(101)的有源面(S1)面向所述第二芯片(102)的有源面(S2);

第一芯片(101)的有源面(S1)包括第一交叠区域(A1)和第一非交叠区域(C1),第二芯片(102)的有源面(S2)包括第二交叠区域(A2)和第二非交叠区域(C2);

第一交叠区域(A1)与第二交叠区域(A2)交叠,第一交叠区域(A1)和第二交叠区域(A2)连接;

第一非交叠区域(C1)与第二走线结构(20)连接;

第二非交叠区域(C2)与第一走线结构(10)连接。

在前不久的华为2021年年报发布会上,华为轮值董事长郭平表示,未来华为可能会采用多核结构的芯片设计方案,以提升芯片性能。同时,采用面积换性能,用堆叠换性能,使得不那么先进的工艺也能持续让华为在未来的产品里面,能够具有竞争力。

值得一提的是,这是华为首次公开确认芯片堆叠技术。也就是说,可以通过增大面积,堆叠的方式来换取更高的性能,实现低工艺制程追赶高性能芯片的竞争力。

限时特惠:本站持续每日更新海量各大内部创业课程,一年会员仅需要98元,全站资源免费下载

点击查看详情

站长微信:Jiucxh

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。