本文是美国IBM奥尔巴尼纳米技术研究中心的先进逻辑路径探索技术高级经理Tenko 在2022年国际电子器件大会(IEDM 2022)上发表的题为《CMOS and for 2nm and 》的演讲,详细阐述了2nm及更先进制程的CMOS技术与创新。

IEDM 2022 主题聚焦

第68届IEEE国际电子器件会议(IEDM)于2022年12月3日至7日在旧金山举行。作为全球顶尖的晶体管及微纳技术突破成果发布平台,2022年IEEE IEDM宣传委员会主席、斯坦福大学电气工程系副教授 表示,"IEEE国际电子器件会议在晶体管发明仅数年后便应运而生,正是基于对其革命性潜力的远见,数十年来,IEEE-IEDM年会发布的突破性成果持续推动着晶体管及相关技术发展,为当今社会数字化转型奠定基础。因此,我们将今年大会主题定为'晶体管问世75周年:应对全球挑战的下一代变革性器件'。"

演讲摘要

2nm节点的晶体管架构

我们开发了适用于2nm及更先进工艺的互补金属氧化物半导体(CMOS)晶体管架构,包括纳米片晶体管()、垂直传输场效应晶体管()以及堆叠式场效应晶体管( FETs)。在前段制程(FEOL)方面,我们通过创新技术提升器件性能,例如降低外部电阻和寄生电容。在后段制程(BEOL)工艺方面,我们采用材料创新和背面供电网络( power )等先进技术,以支持晶体管的持续微缩。

随着传统器件微缩在2005年左右接近极限,器件架构与工艺创新、互连微缩以及材料突破持续推动着技术发展的边界。性能-功耗-面积-成本(PPAC)已成为CMOS微缩的经济性指导原则。要实现CMOS技术的持续微缩,我们仍需多项重大创新。在晶体管架构方面,技术路线已从平面结构()演进至鳍式场效应晶体管(),继而发展到纳米片()、垂直传输场效应晶体管(VTFET)和堆叠场效应晶体管()。自时代以来,有效沟道宽度/鳍片间距(Weff/FP)始终是持续推动CMOS微缩的关键性能调节参数。

电路级性能(包含后段互连负载的布局面积)是评估新型晶体管架构的重要指标。当前横向场效应晶体管( FETs)正面临接触栅极间距(CPP,即CMOS中的晶体管栅极间距)微缩的根本性物理限制。转向垂直传输器件架构后,栅极、侧壁隔离层和接触点都将脱离接触栅极间距(CGP)的限制,从而实现持续微缩——这正是垂直传输纳米片结构(- )的技术突破所在。

垂直传输场效应晶体管(VTFET)相较于微缩版展现出显著的性能优势(约2倍),这得益于其在激进微缩的接触栅极间距(CPP)条件下仍能保持优异的静电特性和寄生参数,而性能则受制于微缩带来的物理限制。相较于垂直纳米线结构,VTFET纳米片凭借显著提升的总有效沟道宽度(Weff),实现了更卓越的性能表现。

通过采用堆叠场效应晶体管( FET)并结合设计工艺协同优化(DTCO)手段,可以实现极具突破性的面积微缩。设计工艺协同优化(DTCO)作为一种先进方法学,能够帮助半导体制造厂在先进工艺开发中降低成本和缩短上市周期。堆叠FET架构的优势在于可独立优化n型与p型场效应晶体管(nFET/pFET),但同时也面临多项工艺挑战:包括超薄氧化物键合、高深宽比接触孔、顶层晶体管的热预算限制,以及需要审慎评估与背面供电网络工艺的兼容性等问题。

前段制程(FEOL)与后段制程(BEOL)工艺创新

在前段制程(FEOL)方面,我们通过多项创新工艺来提升器件性能,其中关键包括降低外部电阻和减少寄生电容。

后段制程(BEOL)创新同样是实现晶体管微缩的关键所在。我们需要在互连集成技术和材料创新方面取得突破:1)后铜时代互连金属候选材料:包括铑(Rh)、铱(Ir)、钼(Mo)、镍(Ni)、钴(Co)和钌(Ru)等。这些新型候选材料必须满足无阻挡层要求(仅需亚纳米级粘附/种子层)。2)替代金属互连方案:复合互连结构已被证明能有效提升整体性能。

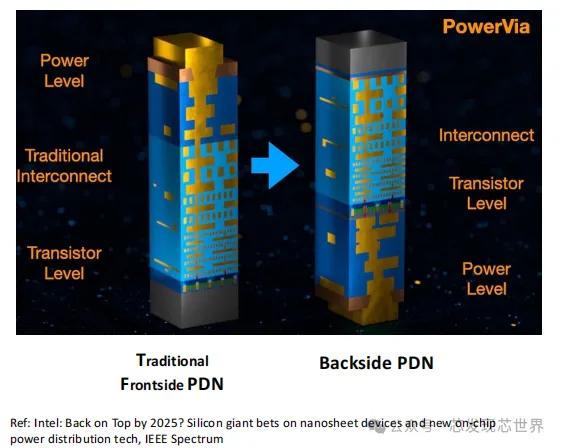

背面供电网络(BSPDN)技术的引入,既能进一步缩小单元高度(cell ),又能保持布线密度不变。该技术还可实现模块级面积微缩(block-level area )并改善IR压降(IR drop)。实际测试表明,BSPDN可带来显著的能效提升,同时使IR压降降低约4至7倍。

晶体管架构创新始终是推动CMOS技术持续微缩的核心驱动力。工艺集成创新则是实现制程节点间PPAC(性能-功耗-面积-成本)持续优化的关键赋能因素。在后段制程(BEOL)中,新材料与新工艺的创新对于最小化电路性能影响至关重要。而背面供电网络技术的应用,不仅显著提升了布线效率,更实现了IR压降的大幅降低。

CMOS工艺微缩历程

随着传统器件微缩于2005年左右趋近物理极限寄生参数寄生参数,器件架构创新、工艺革新、互连技术微缩及材料突破持续推动着摩尔定律的延续。

鲍勃·登纳德(Bob )缩放理论

CMOS工艺微缩的经济学准则

延续CMOS微缩的技术创新路径

晶体管架构创新

CMOS微缩技术的新疆界

2nm及更先进节点的晶体管架构

为何不采用纳米线架构?

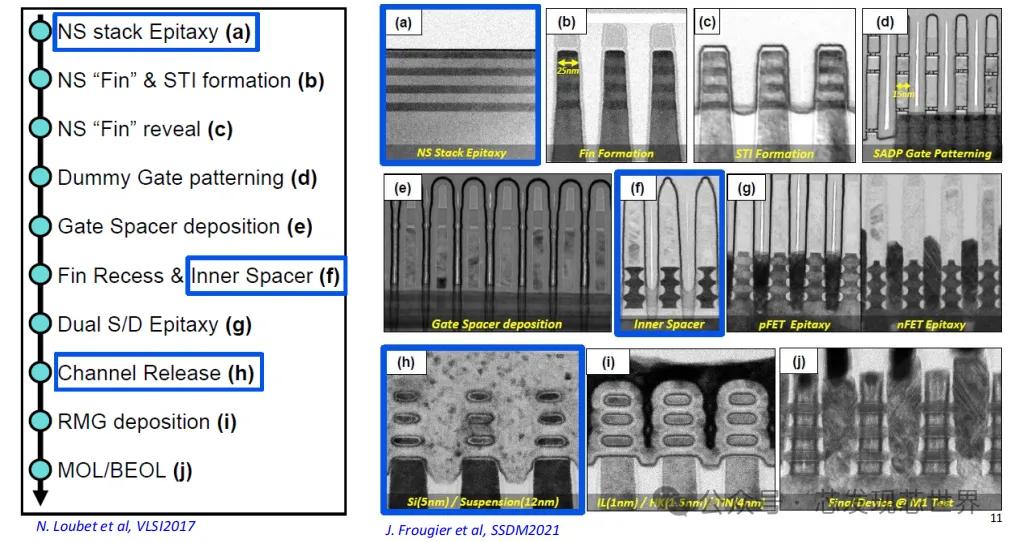

纳米片晶体管工艺流程

纳米片独特模块-内部间隔层

底部介电隔离

纳米片器件性能提升方案(1)——增加堆叠层数

堆叠式场效应晶体管技术(2)——N型与P型器件的双沟道晶向优化

前端制程(FEOL)工艺创新与性能优化

外部电阻的重要性日益凸显

性能的大幅提升使得降低外部电阻(RE

接触电阻优化:通过双硅化物技术调控肖特基势垒高度(SBH)

降低接触电阻率(ρc)的两大关键调控手l

寄生电阻的构成要素与演进趋势

接触沟槽固态外延( SPE):接触电阻率优化技术

激光诱导固态外延(SPE)接触技术的工艺影响

前端制程(FEOL)工艺创新与性能优化

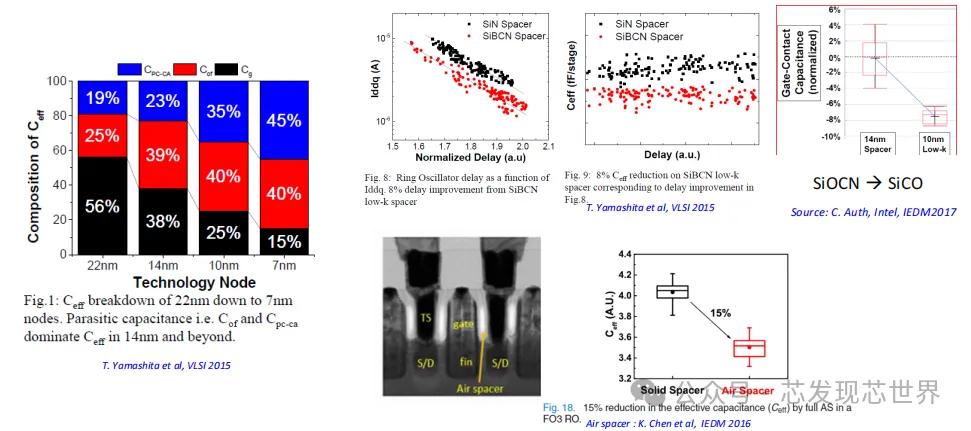

前段制程(FEOL)工艺寄生电容抑制技术

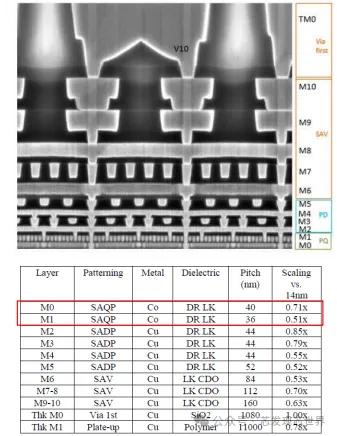

后端制程(BEOL)工艺创新推动晶体管微缩技术

互连集成与材料创新

铜互连扩展的选择性阻挡层技术

铜互连中的选择性阻挡层集成工艺流程

SAM浸泡后的接触角(WCA)变化

选择性阻挡层方案的透射电镜与电子能量损失谱(TEM&EELS)分析

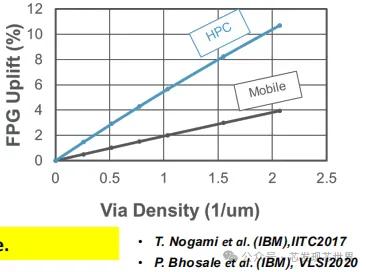

通孔电阻

选择性阻挡层沉积工艺是降低先进铜互连通孔电阻(Via R)的关键技术(S. You et al. (AMAT), )。

后铜互连时代的替代金属候选材料

若干潜在候选材料:铑(Rh)、铱(Ir)、钼(Mo)、镍(Ni)、钴(Co)与钌(Ru)

替代金属互连技术

钴互连技术(英特尔10nm制程应用)

钌(Ru)半大马士革互连技术(比利时Imec微电子研究中心方案)

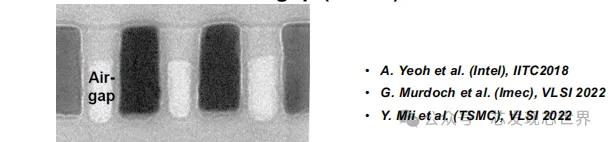

减成法金属工艺+空气隙集成技术(台积电方案)

复合互连( )技术

钴/铜复合互连技术

复合互连技术的能量色散X射线谱(EDX)元素分布表征

导线电阻

通孔电阻

性能提升

后端制程(BEOL)工艺创新推动晶体管微缩技术

为何需要背面供电网络(BSPDN)技术?

背面供电网络(BSPDN: Power )技术

背面供电网络(BSPDN)的核心价值主张

传统正面供电网络(FS PDN)

埋入式电源轨的正面供电网络(FS-BPR PDN)

埋入式电源轨的背面供电网络(BS-BPR PDN)

Arm -A53 CPU模块级研究

总结

致谢

作者衷心感谢IBM研究院众多同事的深刻讨论与鼎力支持。

限时特惠:本站持续每日更新海量各大内部创业课程,一年会员仅需要98元,全站资源免费下载

点击查看详情

站长微信:Jiucxh