集成电路是一个8位串行输入、并行输出的位移缓存器,并行输出为三态输出。常用于单片机和扩展I/O端口。现实教学中,教师往往很困惑,按照传统的看芯片引脚、看时序图等步骤进行学习,学生理解有困难,更不会应用,是一个教学上的难点。如何突破这一难点呢?笔者分析了学生学习困难的原因:

学习障碍之一:芯片引脚众多,名称容易混淆;

人们的认知是一个由浅入深,由表及里的过程。在学习芯片引脚功能的时候,切忌胡子眉毛一把抓。先抓住常规特征和主要特征,由主到次介绍。在教学中,可以分为三步进行:

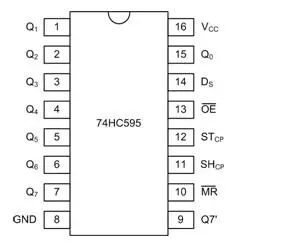

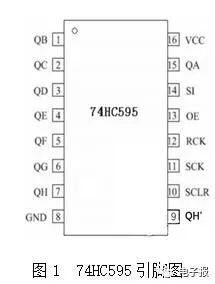

第一步:介绍常规引脚:电源和接地脚及主要特征引脚;

一个数据输入端:DS 14脚;两个数据输出端:串行数据输出9脚QH’和八位并行输出端QA—QH。特别强调两片级联时,第一片的输出引脚接第二片的输入引脚,以完成数据的传输;

第二步:介绍两个时钟引脚11脚SCK、 12脚RCK;具体看图2,发现移位寄存器和存储器分别使用不同的时钟,数据在 SCK(11 脚)的上升沿输入,在RCK(12 脚) 的上升沿进入到存储寄存器中并行输出,所以两个时钟脉冲是互相独立的,能做到输入串行移位与输出锁存的控制互不干扰。

第三步:介绍SCLR移位寄存器清零端10脚和清零端13脚,看图2就可知在何阶段清零。

SCLR为低电平时,移位寄存器的数据清零。通常接到VCC防止数据清零。而G输出使能控制脚,它是低电才使能输出,所以接GND。即两个清零端一正一负:10脚接VCC,13脚接GND。

经过这样有条有理地细细分析,学生就认识了芯片的引脚功能,消除了记忆繁琐困难的心理障碍,为下一步理解打下基础。

学习障碍之二:移位寄存过程抽象,无法理解;

移位输出的过程很抽象,需要学生有些想象力。有时教师用语言描述得再多,也是无济于事,所以教师可以画图3的数据输入输出的仿真图,模拟数据从14脚输入“1111 1110”时Q0-Q7输出的情况。具体过程如下:

第一步:选择数据0 或1 ,准备输入14脚DS端;

第二步:拨开关SW1,即11脚(数据输入时钟)输入一个上升沿74hc595,依次把8位数据输入的移位寄存器,比如数据1111 1000;输入一个数据,就拨开关SW1一次;

第三步:拨开关SW2,即12脚(输出存储器锁存时钟)输入一个上升沿,把输入的8位移入存储寄存器中的数据发送到输出端Q0-Q7中。Q7-Q0所接的led被点亮,说明输出数据分别是1111 1000;

第四步:可以尝试输入其它8位数据,观察它的输出,注意输出顺序。

经过学生的仿真和实验,学生理解了这个芯片的移位显示的原理,说明:从SCK(11 脚)产生一上升沿(移入数据)和RCK(12 脚)产生一上升沿(输出数据)是二个独立过程74hc595,实际应用时互不干扰。即可输出数据的同时移入数据。

学习障碍之三:学习的迁移能力欠缺,表现在如何将几片级联;

在经过一片595显示数据之后,我们可以将两片595级联(如图4):第一块595芯片的串行输出口接第二块595芯片的数据输入口且两片595的11脚和12脚相连,以保证输入移动和输出同步。图4就是两片级联完成16位数据的并行输出。顺序方面第一个写入的数据将会是最后一级级联的输入数据,例如上面的例子是两个级联,第一个写入的是1111 1000它将在最后一个 595 上输出,第二个写的0111 0011它显示在第一个595上。

例如16*16点阵电路中列驱动电路采用了两片移位寄存器进行“级联”,构成列驱动电路,用串行移入、并行输出的方式为16*16点阵显示电子广告屏提供16位列线数据。

这样,我们发现由于只需用到 3 条引线就能实现串行传输数据,我们在51单片机上任意使用3个引脚,分别把它们与 的 11 脚 SCK(串行移位时钟)12 脚 RCK(串行 数据输出)和 14 脚DS(串行数据输入)相连接就可以了。

学习障碍之四:单片机模拟串行外围设备协议通信程序无法理解;

第一个程序:51单片机将8位数据逐位移入的程序:

for (i=0;i位控制

{ SCK=0; //给串行移位时钟送低电平

if((data1&0x80)==0x80) //数据data的最高位为1,则向发送1

SI=1; //发出数据的最高位

else //数据data的最高位为0,则向发送0

SI=0;

data1

限时特惠:本站持续每日更新海量各大内部创业课程,一年会员仅需要98元,全站资源免费下载

点击查看详情

站长微信:Jiucxh